简介

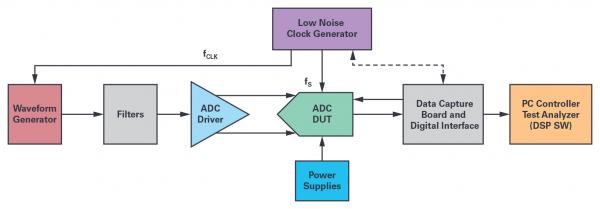

在测试和验证分辨率高于16位的高精度快速模数转换器(ADC)的交流性能时,需要用到近乎完美的正弦波生成器,该生成器至少支持0 kHz至20 kHz音频带宽。通常会使用价格高昂的实验室仪器仪表来执行这些评估和特性表征,例如Audio Precision提供的音频分析仪AP27xx或APx5xx系列。大多数情况下,24位或更高分辨率的现代高速SAR和宽带Σ-Δ ADC都采用单电源和全差分输入,因此要求用于DUT的信号源具备准确的直流和交流性能,同时提供全差分输出(180°错相)。同样,这款交流生成器的噪声和失真水平应该远优于这些ADC的规格,根据大部分供应商提供的规格,其本底噪声水平远低于 –140 dBc,失真水平低于–120 dBc,输入信号音频率为1 kHz或2 kHz,最高可达20 kHz。有关适合高分辨率带宽ADC的典型测试台的典型测试配置,请参考图1。最关键的元件就是正弦波生成器(单信号音或多信号音),其中基于软件的直接数字频率合成器(DDS)可以提供完全的灵活性、极高的频率分辨率和时钟同步性能,利用数据采集系统来执行相干取样,以避免泄漏和FFT窗口滤波。

因为成本只有音频精密分析仪的几分之一,所以能够基于直接数字频率合成(DDFS)原理设计非常精准的正弦波生成器,但需要通过软件在SHARC处理器等浮点DSP处理器上实现。一个相当快的浮点DSP将能满足实时性要求,以及所有算法和处理条件,以达到先进的SAR ADC所设置的失真和噪声性能水平。通过利用SHARC内核架构的全字数据长度(32位或64位定点格式)来实施NCO相位累加,利用专有的40位浮点扩展精度来执行正弦近似函数,以及利用数字滤波器来确定频谱形状,量化效应(回转噪声和截断噪声)得到大幅降低,与用于信号重构的数模转换器(DAC)缺点相比,这种效应可以忽略不计。

直接数字频率合成

1970年4月,Joseph A. Webb1提出了数字信号生成器频率合成器的ZL申请,其中描述了有关DDS生成包括正弦波等各种模拟波形的考虑因素,只需使用数个数字逻辑模块即可实现。之后,Tierney等人2在1971年初发表了论文(后来成为大家频繁引用的参考文献),阐述了通过深化DDS操作进行正交生成来实现直接数字频率生成,以及采样系统理论相关局限性(字词截断和频率规划)问题。随后出现的实际应用大部分依赖于分立式标准逻辑IC,例如TTL 74xx或ECL 10K系列。后来在不到10年的时间里,Stanford Telecom、Qualcomm、Plessey和ADI等纷纷推出了完全集成式解决方案,例如ADI的AD9950和AD9955。这些逻辑IC旨在实现速度、功率和成本之间的最佳平衡,其架构基于查找表(LUT),以确保在有限相位、频率和幅度分辨率下实现相位-正弦幅度转换。如今,ADI公司仍然是DDS独立集成电路的最大供应商,可能也是最独特的供应商,而当前的数控振荡器(NCO)往往都集成到AD9164 或AD9174之类RF DAC中。虽然这些器件在多GHz带宽上具备出色的噪声和线性度性能,但它们都不适合测试中等速度、高分辨率ADC,例如LTC2378-20、AD4020或AD7768。

图1.基于IEEE 1241标准的典型ADC(ac)测试设置的处理链。DDFS能够让整个测量系统完全实现数字化,具备多种优势,包括完全的灵活性和相干取样采集

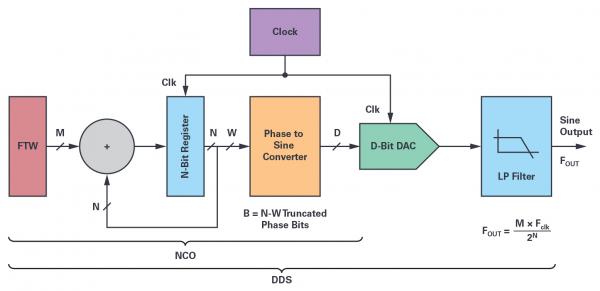

与基于PLL的传统频率合成器相比,NCO和DDS的显著优势包括:极高的频率分辨率、快速灵敏性,以及可轻松生成完美正交的正弦/余弦波形。此外,还提供宽带宽范围和高直流精度。其工作原理受数字信号处理和采样系统理论,数字特性支持对输出信号的相位、频率和幅度实施全数字独立控制。图2所示的框图显示传统DDS的架构,该DDS由三大功能模块组成:

u N位相位累加器;

u 相位-正弦幅度转换器,由W位截取相位输入字表征特性;

u D位DAC及其相关重构滤波器。

相位累加器由简单的N位加法器结合寄存器构成,寄存器的内容按照采样时钟FCLK的速率,以输入相位增量Δθ(通常也称为频率调谐字,FTW)更新。累加器会定期溢出,在采样或参考时钟FCLK和DDS输出频率FOUT之间像小数分频器一样运行,或像齿轮箱一样运行,分频比为:

![]()

溢出速率为生成的波形提供输出频率,使得:

![]()

其中0 ≤ FTW ≤ 2N–1。因为分频器的原因,NCO输出端的参考或采样fS时钟相位噪声的影响会降低

![]()

相位累加器寄存器的输出表示生成波形的电流相位。每个分立式累加器输出相位值然后通过相位-正弦或相位-余弦映射引擎,被转换成幅度正弦或余弦数据或样本。此功能通常利用存储在LUT(ROM)中的三角函数值完成,有时通过执行正弦近似算法完成,或两者组合方式完成。相位-正弦幅度转换器的输出供DAC使用,在滤波之前生成量化和采样正弦信号,使信号平稳,并避免频谱混叠。由DAC有限分辨率导致的幅度量化设定了本底噪声以及相应的频率合成器信噪比(SNR)的理论限值。此外,DAC作为混合信号器件,由于其INL、DNL、压摆率、毛刺和建立时间等特性,展现出一系列直流和交流非线性,这会产生杂散信号音,缩小正弦波生成器的整个动态范围。

基于图2中架构实现的实际正弦波形生成器,主要是相位-幅度转换模块不同,受数字无线电应用这一市场导向影响,该模块通常针对速度和功耗,而不是高精度而优化。实施相位-正弦幅度转换器最简单的方法就是使用ROM,采用一对一映射的方式来存储正弦值。遗憾的是,LUT的长度与相位累加器的宽度N呈指数增长(2N),并且与波表数据字精度W呈线性增长。而且,减小累加器的尺寸或截断其输出之间的权衡和取舍会导致频率分辨率降低,并且严重降低SFDR的性能。结果表明,相位或幅度量化导致的杂散会降低–6 dB/位。实现精细的频率调谐通常需要较大的N,已有几种技术可用来限制ROM的尺寸,同时保持足够的杂散性能。一般会使用简单的压缩方法,利用正弦或余弦函数的四分之一波长对称性将相位幅度范围减小4倍。为了进一步缩小范围,实际会使用截断相位累加器输出的方法,不过这会导致产生杂散谐波。尽管如此,这种方法也因精准的频率分辨率要求、存储器尺寸和成本考量而得到了广泛采用。建议采用多种角分解方法,以降低基于LUT的方法对存储器的要求。与使用各种分段、线性或多项式内插法的幅度压缩结合,在进行需要正弦和余弦函数的I/Q合成时,准确估算正弦函数的第一象限,或按[0, π/4]间隔估算。同样,在没有ROM LUT的情况下,只需要按照逐次逼近的方法调用位移和添加操作,即可使用基于角旋转的方法有效生成复杂信号。这种方法以流行的CORDIC为代表,当硬件乘法器不可用时,或者出于速度或成本考虑,应最大限度减少实施函数所需的栅级数量时(在FPGA或ASIC中),此方法通常比其他方法更快。相反,当硬件乘法器可用时(在DSP微处理器中总是如此),采用插入方法和完整多项式计算(例如泰勒级数展开、切比雪夫多项式)的表查找要比CORDIC更快,尤其是要求高精度时。

图2.NCO的主要功能部分,以及与完整的直接数字频率合成器的区别,其中包括重构DAC和其相关的AAF。NCO部分可用于测试或仿真DAC