三、 电磁兼容的合理PCB设计

随着系统设计复杂性和集成度的大规模提高,电子系统设计师们正在从事100MHZ以上的电路设计,总线的工作频率也已经达到或者超过50MHZ,有的甚至超过100MHZ。当系统工作在50MHz时,将产生传输线效应和信号的完整性问题;而当系统时钟达到120MHz时,除非使用高速电路设计知识,否则基于传统方法设计的PCB将无法工作。因此,高速电路设计技术已经成为电子系统设计师必须采取的设计手段。只有通过使用高速电路设计师的设计技术,才能实现设计过程的可控性。

通常认为如果数字逻辑电路的频率达到或者超过45MHZ~50MHZ,而且工作在这个频率之上的电路已经占到了整个电子系统一定的份量(比如说1/3),就称为高速电路。实际上,信号边沿的谐波频率比信号本身的频率高,是信号快速变化的上升沿与下降沿(或称信号的跳变)引发了信号传输的非预期结果。要实现符合EMC标准的高频PCB设计,通常需要采用以下技术:包括旁路与去耦、接地控制、传输线控制、走线终端匹配等。

(1)旁路与去耦

去耦是指去除在器件切换时从高频器件进入到配电网络中的RF能量,而旁路则是从元件或电缆中转移不想要的共模RF能量。

所有的电容器都是由LCR电路组成,其中L是电感,它与导线长度有关,R是导线中的电阻,C是指电容。在某一频率上,该LC串联组合将产生谐振。在谐振状态下,LCR电路将有非常小的阻抗和有效的RF旁路。当频率高于电容的自谐振时,电容器渐变为感性阻抗,同时旁路或去藕效果下降。因此,电容器实现旁路与去耦的效果受引线长度,以及电容器与器件间的走线、介质填料等的影响。理想的去耦电容器还可以提供逻辑装置状态切换时所需的所有电流,实际上是电源和接地层间的阻抗决定电容器能够提供的电流的多少。

当选择旁路和去耦电容时,可通过逻辑系列和所使用的时钟速度来计算所需电容器的自谐振频率,根据频率以及电路中的容抗来选择电容值。在选择封装尺度是尽量选择更低引线电感的电容,这通常表现为SMT(Surface Mount Technology)电容器,而不选择通孔式电容器(如DIP封装的电容器)。另外在产品设计中,也常常采用并联去耦电容来提供更大的工作频带,减少接地不平衡。在并联电容系统中,当高于自谐振频率时,大电容表现感性阻抗并随频率增大而增加;而小电容则表现为容性阻抗并随频率增加而减少,而且此时整个电容电路的阻抗比单独一个电容时的阻抗要小。

(2)接地系统

大多数电子产品都要求接地。接地是使噪声干扰最小化并对电路进行划分的一个重要方法。接地主要表现在为模拟与数字电路之间提供参考连接以及在PCB的地层和金属外壳之间提供高频连接。

PCB经常包含着危险电压。它包括在电源组件、通信电路、延迟驱动仪表控制、功率交换模块以及类似的器件中。要使产品符合安全规则,并符合电磁兼容性,必须去掉这些危险电压,通常的策略就是采用地线或地平面系统。地线(或地平面)实质是信号回流源的低阻抗路径。由于地线的这种作用,使得地线中可能会有很大的电流存在。因为地线的阻抗不会是零,因而这种电流会产生电位差。当地线中有电位差存在时,对系统的影响就很明显了:地电位差能够造成电路的误动作,使系统工作不正常。

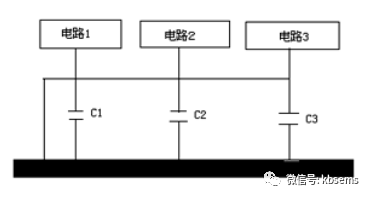

由于接地系统存在地电位差的问题,在设计产品的接地过程中必须针对PCB的特点选择相应的接地方法,而不能随意使用。通常采用的接地方法包括单点接地、多点接地、混合接地等。单点接地是指在产品设计中,接地线路与单独一个参考点相连,这种接地设置目的是为了防止来自两个不同的参考电平的子系统中的电流与射频电流经过同样的返回路径而导致共阻抗耦合。这种接地方法用在低频PCB中比较合适,可以减小分布传输阻抗的影响。但在高频PCB中,返回路径的电感在高频下成为线路阻抗的主要部分,因而在高频PCB中为使接地阻抗最小,通常采用多点接地法。多点接地中最重要的一点就是要求接地引线的长度最小,因为更长的引线代表更大的电感,从而增加地阻抗,引起地电位差。混合接地结构是单点接地和多点接地的复合。当在PCB中存在高低混合频率时常用这种结构,即在低频处呈现单点接地,而在高频处则呈现多点接地。如下图1为容性耦合混合接地。相对应的感性耦合混合接地模型中把C1~C3改为适合的电感即可。